# Thin Film Ceramic Substrate Design Guide

Let's do this.

#### Table of Contents

#### Section 1: Scope

- 1.1: Purpose

- 1.2 Applicability

- 1.3 Applicable Documents

#### Section 2: Introduction to Ceramic Substrates

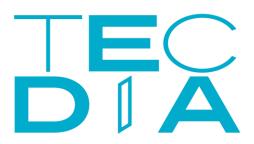

- 2.1: Surface Reference

- 2.2: Useful Vocabulary

#### **Section 3: Circuit Order Requirements**

- 3.1: Required Information for Quote

- 3.2: Required CAD File Format

#### Section 4: Substrate Material

- **4.1: Material Properties**

- 4.2: Thickness Availability

- 4.3: Wafer Layout

#### Section 5: Conductor Layer

- 5.1: Metallization Stack

- 5.2: Selective Plating Process

- 5.3: Conductor Pattern Tolerances

- 5.4: Set Backs and Trace to Edge Circuits

- 5.5: Multiple Surface Conductor Patterns

- 5.6: Other Design Tips

#### **Section 6: Resistor Layer**

- 6.1: Available Resistor Layers

- 6.2: Resistor Design

- 6.3: Power Dissipation

#### Section 7: Predeposited Solder Layer

- 7.1: Available Solder Layers

- 7.2: Solder Pad Design

- 7.3: AuSn Solder Die Attach General Criteria

- 7.4: Solder Dam

#### Section 8: Screening and Reliability

- 8.1: Production Screening

- 8.2: Visual Inspection Criteria

#### **Section 9: Packaging**

- 9.1: Package Types and Availability

- 9.2: Blue Tape Packaging Specifications

# Section 1: Scope

## 1.1: Purpose

This document is intended to provide a guide to designers of thin film substrates. The guide is intended to document the substrate features that can be reliably and economically fabricated in Tecdia's Hybrid Ceramic Technology Group (HCT) based in Cebu Philippines. In many cases, the limits stated herein represent features that have been successfully produced in the past, rather than a fundamental limit on the capabilities of a given process. As more definitive data is obtained on the processes, the procedure will be updated accordingly.

If a designer is able to produce a working design within the limits of this document, he can count on obtaining quality substrates. If the particular needs of a given design fall outside of these limits, the designer should discuss these methods with Tecdia personnel. It may be possible for Tecdia to develop a new process or refine an existing process to achieve the desired results. It also may be decided that the existing processes can support the design even with low yields.

# **1.2:** Applicability

This design guideline manual only applies to thin film ceramic substrates made by the Tecdia thin film ceramic substrate group based in Cebu Philippines.

## **1.3: Applicable Documents**

Tecdia Visual Inspection Criteria Document Tecdia QA screening Document MIL-STD-883: Test Method Standard Microcircuits

# Section 2: Introduction to Ceramic Substrates

## 2.1: Surface Reference

Please reference FIG 2.1.1 for Tecdia's surface reference method for both "flat" and "wrapped" designs.

## 2.2: Useful Vocabulary

*Substrate:* A substance or layer that underlies something, or on which some process occurs, such as a ceramic.

As Fired: A substrate surface condition where the surface receives no treatment after sintering.

Lappe and Polish: The processes used to grind and smooth the surface of a substrate after sintering.

Metallization Layer: The layers of metallization applied to the surface of the substrate.

| Metallization Layer         | Applicable Metals | Purpose                                                                                                                                                                                                                                                                                            |

|-----------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Seed Layer / Adhesion Layer | Ti                | Create strong bond between metal and ceramic                                                                                                                                                                                                                                                       |

| Barrier Layer               | Pt                | An optional metallization layer that protects covered<br>layers from unwanted embrittlement and diffusion<br>from other metals in the metallization stack. Barrier<br>layers usually sit between the seed layer and the<br>conductor layer or between the conductor layer and<br>the solder layer. |

| Conductive Layer            | Au                | Wire bondable (Au only), A high current density conductive layer for passing DC and AC Current.                                                                                                                                                                                                    |

Table 2.2.1: Metallization Stack

*Solder Barrier*: A barrier layer placed to prevent diffusion of solder into another metallization layer. *Wrap:* Metallization connected over the edge of a substrate.

Laser Machining: Laser drilling and cutting performed on the ceramic to creates holes and cut outs

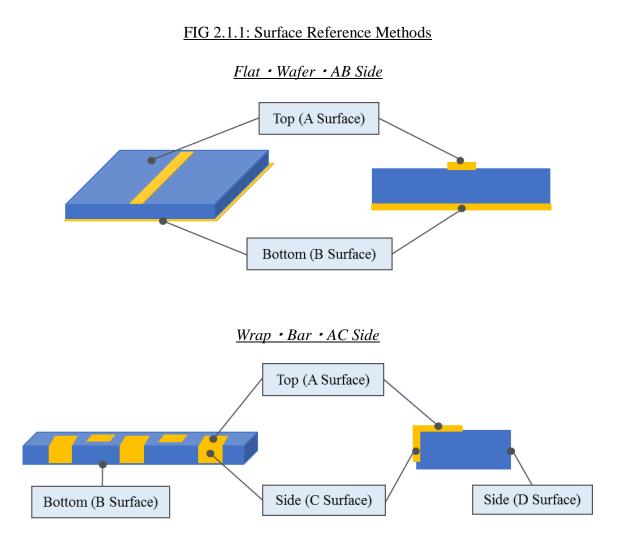

Cut out: A laser machined feature in the substrate with no metallization on the inside walls.

*Plated Via:* A hole with metallization on the inside walls that creates an electrical connection from the top side to the bottom side of the substrate.

*Filled Via:* A plated via hole plugged with some material to prevent solder creep up or increase thermal conductivity.

Side Via: A plated via made at the edge of the substrate

*Recess Wrap:* A wrap made with a recess in the substrate that allows the wrap to be made with a more efficient Post-Cut Laser machining process.

#### Fig 2.2.1: Wraps and Laser Machined Features

Preform Solder: Solder blocks placed and reflowed to attach substrate and component

*Pre-deposited AuSn Solder:* Solder pads that are applied to components and substrates through various deposition methods such as electroplating, evaporation and sputtering.

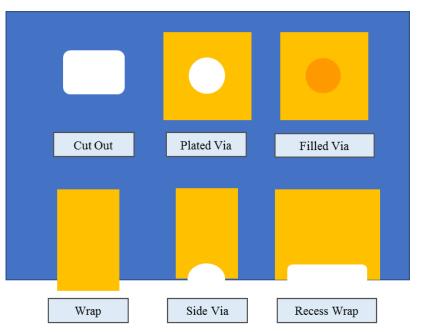

*Air Bridge:* A bridge created in the conductor layer that allows to traces to cross without connecting. Airbridges have no dielectric sitting between the overlapping conductors.

*Polyimide Bridge:* A bridge created in the conductor layer that allows to traces to cross without connecting. Polyimide Bridges have polyimide sitting between the overlapping conductors.

*Solder Dam*: A structure created in the circuit to prevent solder from spreading during reflow. *TaN / Resistor*: Thin Film Resistor structure made from Tantalum Nitride (TaN)

# Section 3: Circuit Order Requirements

# 3.1: Required Information for Quote

Non-CAD Files such as .PDF, .JPEG and .GIF can be sent for quoting only. Production/sample requests require CAD files. In order to quote along a drawing with easily recognizable structures and the information in Table 3.1.1, when applicable, must be provided.

| Specification                                       | Example                                         |  |

|-----------------------------------------------------|-------------------------------------------------|--|

| Substrate Material                                  | Alumina (Al <sub>2</sub> O <sub>3</sub> ) 99.6% |  |

| Surface Finish                                      | Polished: 0.025 µm Ra Max.                      |  |

| Substrate Thickness with Tolerance                  | 0.254 ±0.025 mm                                 |  |

| Chip Size with Tolerance                            | 1±0.05 X 1±0.05 mm                              |  |

| Metallization Stack with Au Thickness and Tolerance | Ti-Pt-Au (1 um Min)                             |  |

| Required Pattern to Pattern Tolerance               | $\pm 25 \ \mu m$                                |  |

| Line and Space Tolerance                            | ± 25 μm                                         |  |

| TaN Sheet Resistance                                | 50 Ω/□                                          |  |

| Tan Resistor Tolerance                              | ± 20%                                           |  |

| AuSn Mixture with Tolerance                         | Au 80%±10%/Sn 20%±10%                           |  |

| AuSn Thickness with Tolerance                       | 5±2 μm                                          |  |

| Via Diameter                                        | 0.2 mm                                          |  |

| Via/ Cut Out Location Tolerance                     | $\pm$ 50 $\mu$ m                                |  |

| Via Diameter Tolerance                              | ± 25 μm                                         |  |

| Quantity to quote                                   | MOQ, 100 pcs & 500 pcs                          |  |

Table 3.1.1: Required Information for Quote

# **3.2: Required CAD File Format**

Please consider the following rules when preparing and sending CAD files for Tecdia's substrate group. CAD files are required for mask production.

- 1. AutoCAD .DWG or .DXF files only. Other CAD extensions such as Gerber and GDS require conversions that can lead to errors and misinterpretations of the drawing.

- 2. AutoCAD .DWG or .DXF file extensions are preferred however, we can also accept any programs DXF output as long as the dimensions are correct and clearly labeled.

- 3. CAD files using metric units are preferred. All Tecdia machines run off of metric units so drawings received in standard units must be redrawn and converted. During conversion critical

dimensions can be changed so converted files must be reviewed for accuracy and approved by the customer before use.

- 4. To create any structure, zero width polylines that create closed polygons are required.

- 5. Avoid overlapping/double structures or protruding lines, as this will lead to file conversion errors and uncertain interpretation of the CAD design.

- 6. All drawings must be drawn in a two dimensional (2D). One 2D drawing is preferred for each surface with patterned metallization. Drawing for each surface may be in the same file, but must be clearly labeled.

- 7. When unclear, metallized areas should be shaded or cross-hatched to indicate where metal is.

- 8. Data or features that are not part of the thin film design should be removed or placed on a separate, reference only layer.

- 9. Tolerance for all critical dimensions should be specified within the drawing.

- 10. Please give each design feature a separate layer. Possible design features include, but are not limited to.

- Substrate Outline/ Chip Outline

- Gold Pattern (A,B,C and D Surface on separate layers)

- Laser machining (Vias and Cut outs)

- Thin Film Resistors (TaN)

- AuSn Pre-Deposited Solder

- Solder Barrier (Pt)

- Solder Dam (Pt)

- Bridges

- 11. For each design feature, please include all required information as explained in each section.

# Section 4: Substrate Material

# **4.1: Material Properties**

All materials Tecdia processes are polished. There are two types of substrates materials that Tecdia processes regularly, Alumina (Al<sub>2</sub>O<sub>3</sub>) and Aluminum Nitride (AlN).

|                                   | Al <sub>2</sub> O <sub>3</sub> 99.6% Polished | AlN 170 W/m*K Polished         |  |

|-----------------------------------|-----------------------------------------------|--------------------------------|--|

| Surface Roughness<br>[µm Ra Max.] | 0.025 (Polished)                              | 0.051 (Polished)               |  |

| Dissipation Factor<br>@ 1MHz      | 0.0001                                        | 0.001                          |  |

| Dielectric Constant<br>[k]        | 9.9                                           | 9.0                            |  |

| Thermal Conductivity<br>[W/m*K]   | 30                                            | 170                            |  |

| Thermal Expansion<br>[10–6/°C]    | 20~300°C: 7<br>20~600°C: 7.2                  | 20~300°C: 4.7<br>20~600°C: 5.2 |  |

Table 4.1.1: Material Properties

Additional available materials include AlN 200 W/m\*K, AlN 230 W/m\*K, Al<sub>2</sub>O<sub>3</sub>96%, Glass, Sapphire, BTO & STO (Titanates), Fused Silica/Quartz. Please inquire for details regarding these materials.

## 4.2: Substrate Thickness Availability

Available wafer sizes and thicknesses for each material are given in Table 4.2.1.

| Substrate Size | Standard Thicknesses                                                                            | Min and Max                               |

|----------------|-------------------------------------------------------------------------------------------------|-------------------------------------------|

| 2"□            | $0.254 \pm 0.0127 \text{ mm}$<br>$0.381 \pm 0.0127 \text{ mm}$<br>$0.635 \pm 0.0127 \text{ mm}$ | Min: 0.1 ± 0.0127 mm<br>Max: 3 mm ± 10%   |

| 4.5"□          | $0.635 \pm 0.0127 \text{ mm}$                                                                   | Min: 0.635 ± 0.0127 mm<br>Max: 3 mm ± 10% |

#### Table 4.2.1: Al<sub>2</sub>O<sub>3</sub> and AlN Available Thicknesses

Wafers thinner than the recommended minimum thickness above can result in substrate warping and cracking which results in lower yields and increased pattern tolerance.

Standard chip dimension:

$L{:}0.25mm{\sim}10.0mm{\times}W{:}0.25mm{\sim}10.0mm{\times}T{:}0.1{\sim}3.0mm$

Any chip size dimension between 0.25mm~40mm is acceptable as long as the following criteria is met.

- Thickness cannot be greater than Length or Width

- Aspect Ratio between Length and Width cannot be greater than 10.

# Section 5: Conductor Layer

# 5.1: Metallization layer

The basic metallization scheme for thin film substrates contains Titanium (Ti), Platinum (Pt) and Gold (Au). This metallization stack is a "fit all" solution since it is optimal for high throughput, cost sensitive, high frequency/data rate and solder or epoxy attach applications.

| Metal | Standard Thickness | Possible Range |

|-------|--------------------|----------------|

| Ti    | 0.06 µm            | 0.03 ~ 0.1 μm  |

| Pt    | 0.15 µm            | 0.05 ~ 0.3 μm  |

| Au    | 1um                | 0.1 ~ 5 μm     |

\*Please contact Tecdia regarding metals and thicknesses outside of range given in table.

# **5.2: Conductor Pattern Tolerances**

For all designs as gold increases maintaining tight tolerances and small features becomes more difficult. Minimum and standard feature limits are given in table 5.2.1 and 5.2.2 for AB and AC designs.

#### Fig 5.2.1: Conductor Tolerances on AB Designs

| Au Thickness  | Standard       | Minimum        | Standard           | Min                |  |

|---------------|----------------|----------------|--------------------|--------------------|--|

| Tru Thickness | Line and Space | Line and Space | Feature Tolerance* | Feature Tolerance* |  |

| ≤2 μm         | 10 µm          | 5 µm           | ±10 µm             | ±5 μm              |  |

| 2~5 µm        | 20 µm          | 10 µm          | $\pm 10 \ \mu m$   | ±5 μm              |  |

| >5 µm         | 20 µm          | 15 μm          | ±25 µm             | ±5 μm              |  |

#### Fig 5.2.2: Conductor Tolerances on AC Designs

| Au Thickness | s Standard Minimum |                | Standard           | Min                |  |

|--------------|--------------------|----------------|--------------------|--------------------|--|

|              | Line and Space     | Line and Space | Feature Tolerance* | Feature Tolerance* |  |

| ≤2 μm        | 25 µm              | 10 µm          | ±15 µm             | ±10 µm             |  |

| 2~5 μm       | 25 µm              | 20 µm          | ±15 µm             | ±15 µm             |  |

| >5 µm        | 25 µm              | 20 µm          | ±25 µm             | ±15 μm             |  |

\*Tolerance only applies to dimensions measured from "Feature to Feature". Dimensions measured from feature to substrate edge must include dicing tolerance. Chip edge to pattern tolerance is 25um Min

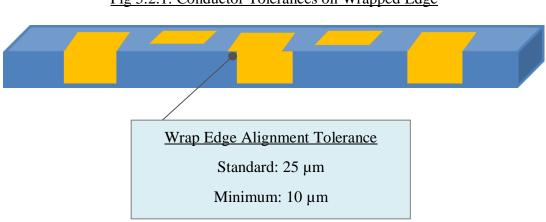

When conductors are connected on two different surfaces, such as an AC wrap design, an extra alignment tolerance must be considered.

#### Fig 5.2.1: Conductor Tolerances on Wrapped Edge

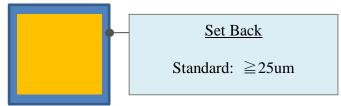

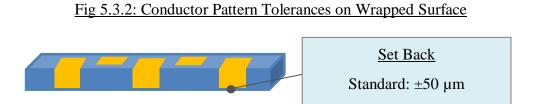

## 5.3: Set Backs and Trace to Edge Circuits

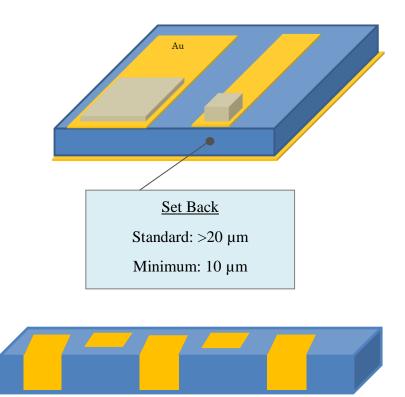

During the substrate sawing process, there is a significant possibility that the substrate metallization will peel if the saw goes through a metallized portion of the circuit. Therefore, a metallization setback should be left between the metal trace and the edge of the circuit whenever possible.

#### Fig 5.3.1: Conductor Pattern Tolerances on Wrapped Surface

On wrapped substrates the traces to edge circuits on the C side are difficult to create due to limitations in resist control on bars. Therefore C side substrates should also maintain a setback between the edge of the C and B side whenever possible. The Setback rules also apply to A, B and D sides with metallization patterns applied.

# 5.4: Multiple Surface Conductor Patterns

Beyond AB and AC patterned substrates, many possible configurations of patterned and fully metallized surfaces in a single design can exist. Table 5.4.1 gives all possible configurations with current Tecdia process.

|            |   | Patterned Surface |             |             |             |   |

|------------|---|-------------------|-------------|-------------|-------------|---|

|            |   | 0                 | 1           | 2           | 3           | 4 |

|            | 0 | OK                | OK          | ОК          | Coming Soon | Х |

| Fully      | 1 | ОК                | OK          | Coming Soon | Х           |   |

| Metallized | 2 | ОК                | Coming Soon | Coming Soon |             |   |

| Surface    | 3 | ОК                | Coming Soon |             |             |   |

|            | 4 | ОК                |             |             |             |   |

Fig 5.4.1: Metallization Configurations

\* Requires review before these configurations can be accepted with Pre-deposited solder layer.

Double Sided pattern AB circuit feature can be realized easily, but maintaining critical dimensions on both sides can be a challenge. Minimum Front to Back Tolerance for patterns is  $\pm 5$ um.

# **5.5: Other Design Tips**

#### Avoid Acute Angles

In the mask creation process, the patterns are formed on the mask using rectangular flashes of light. Certain patterns, especially acute angles, require numerous flashes to form. This can result in over exposure which creates bleeding in these areas of the mask.

#### Avoid Circular Structures

Circular and round structures cannot keep tight tolerances when compared to straight features with right angles. To keep processing time and cost down, it's best to avoid circular structures when possible.

#### Keep Gold Thickness Constant Throughout All surfaces

Having areas of the electrode where the gold thickness is different requires extra lithography and etching processes. The extra steps and defects that occur during the extra steps add unnecessary cost and so varied gold thickness should be avoided when possible.

# Section 6: Resistor Layer

# 6.1: Available Resistor Layers

The resistors formed at Tecdia are normally formed from Tantalum Nitride (TaN) in one of three standard sheet resistivity layers as described in Table 6.1.1.

| TaN Ω/□ Value       |

|---------------------|

| $25\Omega/\square$  |

| $50 \Omega / \Box$  |

| $75\Omega/\square$  |

| $100\Omega/\square$ |

Table 6.1.1: Available Resistor Layers

Tecdia resistor layers maintain characteristics given in Table 6.1.2

| Table 6.1.1: Resistor Layer Characteristics |

|---------------------------------------------|

|---------------------------------------------|

| Temperature Coefficient of Resistance | -100±50ppm (-55~125°C)   |

|---------------------------------------|--------------------------|

|                                       | 125°C , 1000 hours       |

| Thermal Life Test                     | Max change in resistance |

|                                       | still under evaluation   |

## **6.2:** Power Dissipation

No definitive studies have been performed to test the long-term reliability of the resistors built at Tecdia. Instead the below table gives figures that are commonly accepted in the thin film industry. There are a lot of parameters that will affect the power rating sop If you circuit has poor heat sinking use the more conservative value, while conversely, circuits with good heat sinks can use the least conservative numbers.

| Fig 6.2.1: Power Dissipation by | Area |

|---------------------------------|------|

|                                 |      |

| Most Conservative (Mil Spec and Space Applications) | 50 Watts per square inch   |

|-----------------------------------------------------|----------------------------|

| Typical                                             | 400 Watts per square inch  |

| Least Conservative                                  | 1200 Watts per square inch |

\* Above table does not represent Tecdia measured values

# Section 7: Pre-Deposited Solder Layer

# 7.1: Available Solder Layers

Pre-Deposited Solder Pads are formed from AuSn through an electroplating process with characteristics given in Table 7.1.1.

| Table | 7.1.1: | Plated | AuSn | Specs |

|-------|--------|--------|------|-------|

|       |        |        |      |       |

| AuSn Ratio           | Au 80%; Sn 20%, Au 70%; Sn 30%     |

|----------------------|------------------------------------|

| AuSn Ratio Tolerance | ±10%(TBD)                          |

| Thickness Range      | 3~7 μm (5 μm Standard)             |

| Thickness Tolerance  | ± 1μm(3~4 μm),<br>±2 μm (4.1~7 μm) |

| Reflow Temperature   | 320°C                              |

All solder pads sit on top of a conductor layer.

# 7.2: Solder Pad Design

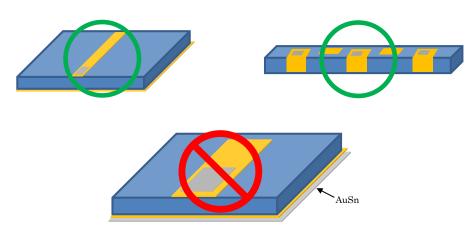

AuSn Pre-deposited solder can be applied to a single side of either flat or wrapped designs.

Fig 6.2.1: Available Resistor Configurations

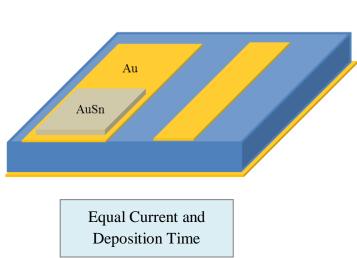

All solder pads sit on top of the conductor layer. To avoid problems with small misalignments between the gold and solder patterns the solder pads need to have a setback as seen in Fig. 7.2.1

Electroplated AuSn deposits as a function of current and area. When solder pads on the same surface have great variance in area it is very difficult to control the thickness for both pads. In cases where solder pad thickness is critical, electrodes with different areas should be avoided.

# 7.3: AuSn Solder Die Attach General Criteria

- a. Preheat components to within 150 to 200°C of the eutectic temperature of the solder pad material before performing die attach.

- b. Solder pad should be same dimensions as the bottom electrode of the component, with thickness sufficient to insure proper attachment.

- c. Typically, die-attach processing should be done under an atmosphere of  $H_2N_2$  forming gas, 90 to 95 % N<sub>2</sub> with 5 to 10 % H<sub>2</sub>. (Hydrogen serves a reducing agent for thin surface oxides.)

- d. With the solder pad in its molten state, quickly place the die on the preform (if not done before) and scrub it lightly with tweezers for 2 to 3 seconds.

- e. After attaching die, remove the assembly from the die-attaching station and allow it to cool gradually.

- f. Solder attach is strongest when performed on fully metalized electrodes containing Pt barrier layer.

- g. Tecdia Al2O3 substrates with sputtered and plated metallization can withstand high temperature (400°C) die-attach conditions without physical damage for most metal stacks. Tecdia AlN substrates with sputtered and plated metallization can withstand high temperature (400°C) die-attach conditions without physical damage as long as the Au thickness is 2um±20% or less.

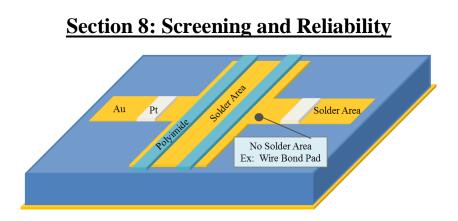

# 7.4: Solder Dam

Solder Dams are barriers that prevent solder from flowing into unwanted area. There are numerous dielectrics and metals that can be applied to create solder dams. Tecdia Solder dams are normally formed using Platinum or Polyimide.

Pt Solder Dam Thickness: TBD

# **8.1: Production Screening**

Tecdia performs the screening on its substrates as given in table 8.1.1 when applicable.

| Test                    | Test Criteria                                                                            | Sampling Quantity                            | Applicable Designs                 |

|-------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|

| Visual Inspection       | MIL-STD-883,<br>Method 2032, Class H                                                     | MIL-STD-105E level II<br>Normal 1.0%         | All Designs                        |

| Wire Bond Pull          | Pull Strength : ≧5g of force,<br>Wire diameter : 25μm                                    | A side only<br>1pcs / Lot<br>or Monitor chip | Any Design with<br>Conductor Layer |

| Heat Resistance Test    | 400°C for 5 minutes (Alumina)<br>300°C for 5 minutes (AlN)<br>Substrates with AuSn : TBD | 1pcs / Lot<br>or Monitor chip                | Any Design with<br>Conductor Layer |

| Metallization Thickness | -                                                                                        | 3pcs / Lot<br>or Monitor chip                | Any Design with<br>Conductor Layer |

| Chip Dimensions         | -                                                                                        | 3pcs / Lot<br>or Monitor chip                | All Designs                        |

| Substrate Thickness     | -                                                                                        | 3pc / Lot                                    | All Designs                        |

| Table 8.1.1: Substrate Screening |

|----------------------------------|

|----------------------------------|

# 8.2: Lot Definition

Lot numbers are assigned using the following steps

- 1. Lot number is assigned to parts A side sputtered together

- 2. Multiple part numbers cannot be sputtered together

- 3. All processes proceeding A side sputter cannot have mixed lots

\*For internal traceability an additional internal lot number is assigned to every 10 sticks plated together.

# 8.2: Standard Visual Inspection Criteria

# Inspection Standard: Mil-STD-105E Level II Normal 1%

Microscope at 20X, only inspect metallized areas

| Inspection Item                                                                            | Acceptance Criteria                                                                         | Example        |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------|

| Excess Metallization<br>Residual Metallization in<br>gap region.                           | ■Not allowed if it reduces the original separation between adjacent patterns by 50% or more |                |

| Metallization Deficit<br>A deficit in the designed<br>pattern metallization                | ■Not allowed if larger than 50% of metallization width for most traces                      | Pass Fail Fail |

| Peeling Metallization<br>Peeling of metallization<br>exposing non-Au layers or<br>sapphire | ■Not Allowed                                                                                | Fail           |

| Metallization Defect<br>Au protruding from<br>metallization surface                        | <ul> <li>Not allowed if diameter is over 30<br/>μm</li> </ul>                               | Pass Fail      |

| Adhered Foreign Metal<br>Any adhered metal other<br>than Au                                | Not allowed if connecting critical areas                                                    | Fail<br>Pass   |

| <u>Adhered Foreign</u><br><u>Contamination</u><br>Any non-metal<br>contamination           | ■ Not allowed                                                                               | Fail           |

| Pattern Offset<br>Misalignment between<br>connecting pattern on wrap<br>edge         | <ul> <li>Not allowed if offset is greater than 25µm</li> </ul>                                          |           |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------|

| Scratch<br>Any adhered material other<br>than Au                                     | ■Scratches exposing underlayer not allowed.                                                             | Pass Fail |

| <u>Crack</u><br>Crack in sapphire, epitaxy,<br>metallization or<br>passivation.      | ■ Not allowed                                                                                           | Fail      |

| <u>Chipping</u><br>Missing fragments of chip<br>broke off during<br>singulation.     | Not allowed if chipping extends<br>under the pattern. Chipping just<br>touching the pattern is allowed. | Pass      |

| Discoloration<br>Abnormal Color caused by<br>residual chemicals and<br>contamination | ■ Not allowed                                                                                           | Fail      |

\* Visual Inspection Criteria can be customized per customer request.

# Section 9: Packaging

## 9.1: Package Types and Availability

Waffle packs are available for all substrate configurations. Blue Tape Packaging availability depends on chip please consult Tecdia personnel for blue tape options.

Substrates on Blue Tape cannot exceed 1.2mm in Length of Width due to inspection limitations.

## 9.2: Blue Tape Packaging Specifications

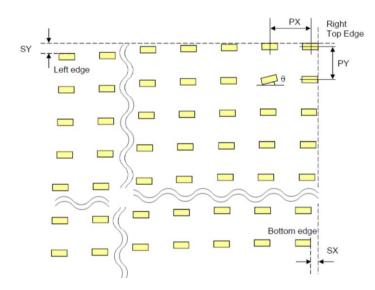

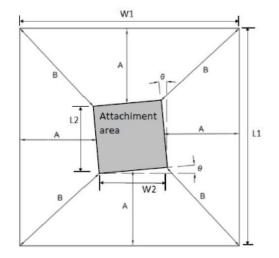

Chips placed on blue tape can be shifted and rotated within the limited defined in Fig and Table 9.2.1.

#### Fig 9.2.1: Blue Tape Chip Alignment

| Acronym |                                         | Standard Value               |

|---------|-----------------------------------------|------------------------------|

| PX      | Distance between chips (X Axis)         | $\pm 0.10 \text{ mm}$        |

| PY      | Distance between chips (Y Axis)         | ± 0.10 mm                    |

| SX      | Distance between chip and Edge (X Axis) | 0.40 mm MAX                  |

| SY      | Distance between chip and Edge (Y Axis) | 0.40 mm MAX                  |

| θ       | Chip rotation angle vs. X axis          | $\pm 10^{\circ} \text{ MAX}$ |

#### Table 9.2.1: Blue Tape Chip Alignment

Blue Tape sheet and alignment are come shipped as shown in Fig and Table 9.2.2.

Fig 9.2.2: Tape Alignment Area

## Table 9.2.2: Tape Alignment Area

| Acronym |                                          | Standard Value               |

|---------|------------------------------------------|------------------------------|

| L1      | Length of Entire Blue Tape Package       | $200 \pm 5 \text{ mm}$       |

| W1      | Width of Entire Blue Tape Package        | 200 ± 5 mm                   |

| L2      | Length of Alignment area                 | Max 70mm ± 0.5 mm            |

| W2      | Width of Alignment area                  | Max 70mm ± 0.5 mm            |

| Α       | Alignment Area to Tape Edge              | 60 mm Min                    |

| В       | Alignment Area to Tape Corner            | 90 mm Min                    |

| θ       | Alignment Area rotation angle vs. X axis | $\pm 10^{\circ} \text{ MAX}$ |

# 9.3: Blue Tape Packaging Material

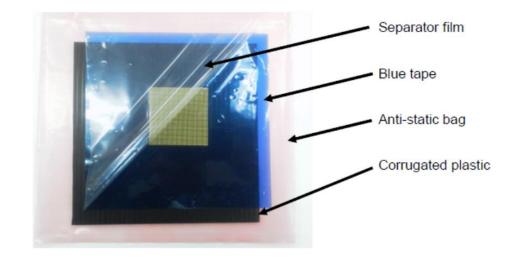

Blue Tape parts are packaged and shipped as shown in Fig 9.3.1.

Tecdia packaging is compliant with EU Packaging and Packaging Waste directive for package materials (Blue tape)

Drafted by Daniel Young

Tecdia Co.,Ltd.

F-002-1 (NOV)